The first in the projects for the BeMicro CV board will be a HW LED flasher. Although the design is very easy, it is a complete design including absolutely all the elements needed to achieve a reliable design with timing closure.

For an introduction about the Be Micro CV evaluation board, please refer to this post.

What will the project do:

- Flash a sequence of LEDs by dividing the clock input

- Make a ‘lamp test’ (all LEDs lit) when reset is pressed

- LEDs sequence is accelerated if the user presses the second push button on the board.

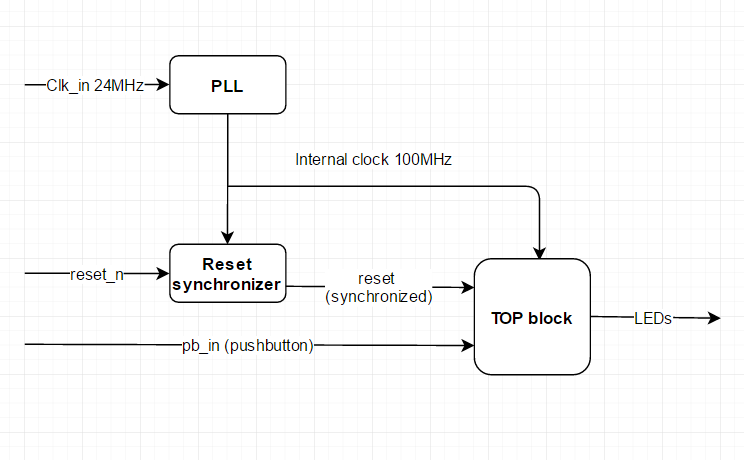

The design includes the following blocks:

- PLL: Takes the 24MHz input to the board and generates an internal 100MHz clock signal.

- Reset synchronizer: Reset signal is sampled by this block using two flip-flops. Reset is released only on rising edge of internal 100MHz clock. This is the recommended reset connection by Altera for avoiding recovery and removal timing failures. Actually the result is to connect a synchronized reset to the async. reset input of all FFs in the design.

- top block: Includes a counter to divide the input frequency to blink the LEDs at a speed visible to humans. Also takes care of reset treatment (all LEDs lit) and of LEDs blink acceleration.

The design also includes the following files:

- QSF including pin assignment

- SDC – Timing constraint file

- vhdl source files

- qip files for Altera generated IP sources

Design directories structure:

- quartus: project files, .qsf file, .sdc file

- src

- top.vhd and reset_sync.vhd source files

- ip directory

- pll1 directory

- files generated by Altera IP Wizard for ‘pll1’ (24MHz -> 100 MHz)

- pll1 directory

The design was generated using Quartus Prime 15.1. The project archive file (.qar) is available here.

If you want to test the design without compiling it first, you can download the .sof file here.