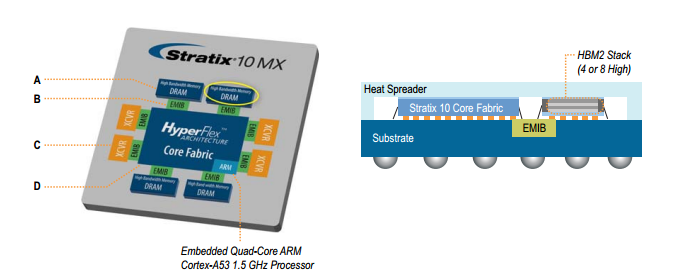

The Stratix® 10 MX DRAM system-in-package (SiP) family combines a 1 GHz high-performance monolithic FPGA fabric, state-of-the-art Intel Embedded Multi-die Interconnect Bridge (EMIB) technology, and High Bandwidth Memory 2 (HBM2), all in a single package (SiP).

The blue DRAM boxes (A), show the HBM2 memory tiles that the device integrates in package (up to 4 tiles integrated per package). Each HBM2 memory tile is either 4 or 8 memory layers high and supports up to 16 independent channels (64 bits each). Each channel can run at data rates of up to 2 Gbps and provide up to 16 GBps of aggregate bandwidth per channel.

The green boxes(B), represent Intel’s EMIB technology, which enables integration of different tiles alongside a the monolithic FPGA core fabric. The EMIB interface supports the required interface data rates between the core fabric and the HBM2 memory tile. This interface is compatible with standard JEDEC and IEEE 1500 specifications.

The orange boxes(C), represent transceiver tiles that connect to the monolithic core fabric using Intel’s EMIB technology.

The high-performance monolithic core fabric (D) is built using the HyperFlex architecture. This core fabric can run up to 1 GHz and provide up to 2X performance gains compared to previous generation high-end FPGAs.

Stratix 10 MX Key Benefits

Higher Memory Bandwidth

The Stratix 10 MX integrates up to four HBM2 tiles and a high-performance FPGA fabric in a single package. Each HBM2 tile provides up to 256 GBps of aggregate bandwidth. Stratix 10 MX devices thus provide up to 1 TBps (1,024 GBps) aggregate bandwidth in a single package. This bandwidth enables multiple applications such as machine learning, data analytics, image recognition, workload acceleration, 8K video processing, and high-performance computing.

Lower Power

Stratix 10 MX devices provide lower power compared to conventional DDR solutions. For example, to meet 128 GBps of memory bandwidth, a system designer would need roughly 5 DDR4 (3,200 Mbps, 4 Gb) DIMM devices, with each consuming around an estimated 4 W (I/O + PHY + controller + memory) for a total estimated power of 22 W (assuming 30% read, 30% write, single rank configuration). A single Stratix 10 MX device provides equivalent memory bandwidth at approximately half the power. This power savings is due to lower I/O power (short trace to EMIB vs. long PCB trace), lower data rates, and 3D DRAM stacking efficiencies.

Smaller Form Factor, Reduced Board Complexity, and Ease of Use

Stratix 10 MX devices provide up to 1 TBps of bandwidth in a single package, resulting in substantial form factor savings. A single Stratix 10 MX device provides equivalent bandwidth at a fraction of the form factor size, resulting in 15X form factor savings on average, compared to solutions using DDR4 DIMM devices.

This form factor savings frees critical board space, which gives designers flexibility to add more functionality or make better system-level performance or power trade off decisions. Eliminating DDR4 PCB routing results in lower board complexity (routing and layer count), improved signal and power integrity, and lower BOM and assembly cost.

For more information:

Stratix 10 MX: 1 TBps Memory Bandwidth in a Single FPGA

White Paper: Stratix 10 MX Devices Solve the Memory Bandwidth Challenge